📌 TOPINDIATOURS Eksklusif ai: ByteDance Introduces Astra: A Dual-Model Architectur

The increasing integration of robots across various sectors, from industrial manufacturing to daily life, highlights a growing need for advanced navigation systems. However, contemporary robot navigation systems face significant challenges in diverse and complex indoor environments, exposing the limitations of traditional approaches. Addressing the fundamental questions of “Where am I?”, “Where am I going?”, and “How do I get there?”, ByteDance has developed Astra, an innovative dual-model architecture designed to overcome these traditional navigation bottlenecks and enable general-purpose mobile robots.

Traditional navigation systems typically consist of multiple, smaller, and often rule-based modules to handle the core challenges of target localization, self-localization, and path planning. Target localization involves understanding natural language or image cues to pinpoint a destination on a map. Self-localization requires a robot to determine its precise position within a map, especially challenging in repetitive environments like warehouses where traditional methods often rely on artificial landmarks (e.g., QR codes). Path planning further divides into global planning for rough route generation and local planning for real-time obstacle avoidance and reaching intermediate waypoints.

While foundation models have shown promise in integrating smaller models to tackle broader tasks, the optimal number of models and their effective integration for comprehensive navigation remained an open question.

ByteDance’s Astra, detailed in their paper “Astra: Toward General-Purpose Mobile Robots via Hierarchical Multimodal Learning” (website: https://astra-mobility.github.io/), addresses these limitations. Following the System 1/System 2 paradigm, Astra features two primary sub-models: Astra-Global and Astra-Local. Astra-Global handles low-frequency tasks like target and self-localization, while Astra-Local manages high-frequency tasks such as local path planning and odometry estimation. This architecture promises to revolutionize how robots navigate complex indoor spaces.

Astra-Global: The Intelligent Brain for Global Localization

Astra-Global serves as the intelligent core of the Astra architecture, responsible for critical low-frequency tasks: self-localization and target localization. It functions as a Multimodal Large Language Model (MLLM), adept at processing both visual and linguistic inputs to achieve precise global positioning within a map. Its strength lies in utilizing a hybrid topological-semantic graph as contextual input, allowing the model to accurately locate positions based on query images or text prompts.

The construction of this robust localization system begins with offline mapping. The research team developed an offline method to build a hybrid topological-semantic graph G=(V,E,L):

- V (Nodes): Keyframes, obtained by temporal downsampling of input video and SfM-estimated 6-Degrees-of-Freedom (DoF) camera poses, act as nodes encoding camera poses and landmark references.

- E (Edges): Undirected edges establish connectivity based on relative node poses, crucial for global path planning.

- L (Landmarks): Semantic landmark information is extracted by Astra-Global from visual data at each node, enriching the map’s semantic understanding. These landmarks store semantic attributes and are connected to multiple nodes via co-visibility relationships.

In practical localization, Astra-Global’s self-localization and target localization capabilities leverage a coarse-to-fine two-stage process for visual-language localization. The coarse stage analyzes input images and localization prompts, detects landmarks, establishes correspondence with a pre-built landmark map, and filters candidates based on visual consistency. The fine stage then uses the query image and coarse output to sample reference map nodes from the offline map, comparing their visual and positional information to directly output the predicted pose.

For language-based target localization, the model interprets natural language instructions, identifies relevant landmarks using their functional descriptions within the map, and then leverages landmark-to-node association mechanisms to locate relevant nodes, retrieving target images and 6-DoF poses.

To empower Astra-Global with robust localization abilities, the team employed a meticulous training methodology. Using Qwen2.5-VL as the backbone, they combined Supervised Fine-Tuning (SFT) with Group Relative Policy Optimization (GRPO). SFT involved diverse datasets for various tasks, including coarse and fine localization, co-visibility detection, and motion trend estimation. In the GRPO phase, a rule-based reward function (including format, landmark extraction, map matching, and extra landmark rewards) was used to train for visual-language localization. Experiments showed GRPO significantly improved Astra-Global’s zero-shot generalization, achieving 99.9% localization accuracy in unseen home environments, surpassing SFT-only methods.

Astra-Local: The Intelligent Assistant for Local Planning

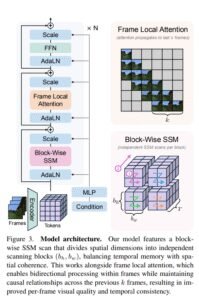

Astra-Local acts as the intelligent assistant for Astra’s high-frequency tasks, a multi-task network capable of efficiently generating local paths and accurately estimating odometry from sensor data. Its architecture comprises three core components: a 4D spatio-temporal encoder, a planning head, and an odometry head.

The 4D spatio-temporal encoder replaces traditional mobile stack perception and prediction modules. It begins with a 3D spatial encoder that processes N omnidirectional images through a Vision Transformer (ViT) and Lift-Splat-Shoot to convert 2D image features into 3D voxel features. This 3D encoder is trained using self-supervised learning via 3D volumetric differentiable neural rendering. The 4D spatio-temporal encoder then builds upon the 3D encoder, taking past voxel features and future timestamps as input to predict future voxel features through ResNet and DiT modules, providing current and future environmental representations for planning and odometry.

The planning head, based on pre-trained 4D features, robot speed, and task information, generates executable trajectories using Transformer-based flow matching. To prevent collisions, the planning head incorporates a masked ESDF loss (Euclidean Signed Distance Field). This loss calculates the ESDF of a 3D occupancy map and applies a 2D ground truth trajectory mask, significantly reducing collision rates. Experiments demonstrate its superior performance in collision rate and overall score on out-of-distribution (OOD) datasets compared to other methods.

The odometry head predicts the robot’s relative pose using current and past 4D features and additional sensor data (e.g., IMU, wheel data). It trains a Transformer model to fuse information from different sensors. Each sensor modality is processed by a specific tokenizer, combined with modality embeddings and temporal positional embeddi…

Konten dipersingkat otomatis.

🔗 Sumber: syncedreview.com

📌 TOPINDIATOURS Hot ai: ARM explained: How a chip designer became central to moder

Humanoid robots, autonomous vehicles, smartphones, smart home devices, and even something as mundane as a TV remote or a coffee machine all share a quiet commonality. At the heart of most of this technology sits a processor built on designs created by one company. Arm. Unlike most household tech giants, ARM does not manufacture physical chips. Yet it has become one of the most influential forces in modern computing, shaping how billions of devices think, calculate, and conserve power.

As companies like Qualcomm push ARM-based processors into Windows laptops, and as Apple continues to redefine performance expectations with its M-series chips, the industry appears to be entering one of the most significant computing transitions in decades.

At the same time, emerging fields such as robotics, autonomous driving, and artificial intelligence are making energy efficiency just as important as raw performance. This is where ARM’s capabilities and long-standing design philosophy become central to the future of computing.

A world built on ARM

ARM’s reach is far broader than most people realize. Nearly every modern smartphone relies on ARM-based processor designs, and ARM technology also helps a growing share of automotive electronics, smart appliances, industrial automation systems, and embedded devices. Almost anyone watching a technology video today is likely within arm’s reach of a device powered by an ARM-based chip.

This dominance did not happen by accident. ARM’s architecture became the foundation of mobile computing long before smartphones existed, and that early foothold shaped how software ecosystems evolved. As operating systems and applications were built specifically for ARM processors, a powerful feedback loop emerged. More devices led to more developers, which in turn reinforced ARM’s central role.

What a processor actually does

At its core, a processor is a computing engine that executes instructions to complete tasks. The most important of these processors is the central processing unit, or CPU, which runs operating systems and applications. Although CPUs today appear impossibly complex, their fundamental behavior is surprisingly simple.

A CPU is essentially a massive collection of electronic switches. These switches operate using binary logic, where information is represented as ones and zeros. The physical component responsible for this switching behavior is the transistor, most commonly a field-effect transistor. When a transistor detects an electrical signal, it outputs a one. When it does not, it outputs a zero. By combining billions of these switches, a processor can perform calculations, make decisions, and coordinate data movement.

Processors constantly exchange data with memory. Long-term storage is handled by drives, while short-term working data lives in random access memory, or RAM. Inputs from peripherals such as keyboards, touchscreens, and sensors feed into this system, allowing software instructions to interact with the real world.

From mechanical calculators to silicon logic

The basic idea behind computing predates electronics by centuries. Early mechanical calculators relied on gears and rotating components to perform arithmetic. Each gear represented a digit, and clever mechanical linkages handled operations such as carrying values from one digit to the next. While modern CPUs are vastly more complex, the conceptual similarity remains. Simple operations are combined into systems capable of solving far more complicated problems.

The key difference is that electronic processors operate in binary rather than decimal. Because transistors only recognize two states, numbers are represented using sequences of ones and zeros. Calculations require frequent carry operations, but the simplicity of binary logic allows it to be implemented extremely efficiently at microscopic scales.

ARM’s role: architecture, not manufacturing

What makes ARM unusual is not what it builds, but what it chooses not to build. Unlike companies such as Intel, ARM does not manufacture chips. Instead, it creates the architectural “rulebook” that defines how a processor works. These designs are delivered as code that describes how to construct a CPU, which is then manufactured by partner companies such as TSMC.

This rulebook has two key layers. One is the microarchitecture, which describes the physical layout and behavior of a processor core. Designs such as ARM’s Cortex series fall into this category. The other is the instruction set architecture, or ISA, which defines the instructions a processor understands and how software communicates with hardware. ARM’s ISA acts as a stable contract between chip designers and software developers, ensuring compatibility across a vast ecosystem.

Because ARM licenses its designs, multiple companies can integrate ARM technology into a single system-on-a-chip, or SoC. A modern smartphone SoC combines CPUs, graphics processors, AI accelerators, modems, and specialized controllers onto one piece of silicon, enabling faster communication and improved energy efficiency.

Customization and compatibility

ARM’s licensing model allows partners to innovate while remaining compatible with the broader ecosystem. Some companies use ARM’s CPU designs directly, while others build their own custom cores that still adhere to ARM’s instruction set. Qualcomm’s Snapdragon processors are a prominent example of this approach, combining ARM compatibility with proprietary microarchitectural choices to balance performance and efficiency.

This flexibility has enabled ARM-based processors to evolve rapidly in line with market demands. In mobile devices, manufacturers sought maximum performance without sacrificing battery life. ARM’s low-power design philosophy made it the logical choice, and its architecture became deeply embedded in mobile operating systems and applications.

A Cambridge origin story

ARM’s focus on efficiency dates back to its origins in Cambridge, UK. The company emerged as a spin-off from Acorn Computers, where engineers were tasked with developing a processor that could operate within strict power and thermal constraints. This constraint forced a radically different design approach, prioritizing simplicity and efficiency over brute force.

The early ARM processor adopted a reduced instruction set philosophy, executing simpler instructions more efficiently. One of its first high-profile uses was in the Apple Newton, an early handheld device that required strong performance within a limited power envelope. Although the Newton itself was not a commercial success, it helped establish ARM’s technical credibility.

To survive beyond that initial project, ARM adopted a licensing model that allowed other companies to use its processor designs. This decision laid the foundation for ARM’s expansion into countless products and industries.

<h2 class="wp-block-heading" id="h-smartphones-and-the-softwar…

Konten dipersingkat otomatis.

🔗 Sumber: interestingengineering.com

🤖 Catatan TOPINDIATOURS

Artikel ini adalah rangkuman otomatis dari beberapa sumber terpercaya. Kami pilih topik yang sedang tren agar kamu selalu update tanpa ketinggalan.

✅ Update berikutnya dalam 30 menit — tema random menanti!